Logiksynthese mit Funktionaler Dekomposition

| project staff | project description | publications

|

| Chair of Computer Architecture | |

| Christoph Scholl, Prof. Dr. | |

The basic problem when designing a circuit is to convert a given circuit specification into a correct circuit implementation. A partial stage of this design flow is logic synthesis which generates an appropriate implementation starting from the specification which the functional layout provides. The result of the logic synthesis is a netlist description using a library of basic cells.

The main topics treated in this project basically belongs to combinational logic synthesis, which means the automatic synthesis of combinational partial functions (without registers).

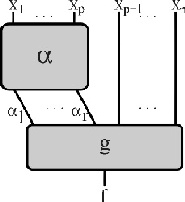

The analyzed method for multi-level combinational logic synthesis is based on recursive decomposition of the boolean function to be realized. A disjoint decomposition of a boolean function f with the input variables x1, …, xn is a construction of the following form:

Now the blocks specified by alpha and g are decomposed recursively. In order to reduce the costs of the realization solutions which have a small number of partial functions are desireable.

One application of the proposed method is (but not exclusively) the synthesis of LUT (=look up table)-based FPGAs, for which boolean functions can be realized up to a certain amount of inputs by a single look up table. The main characteristics of the decomposition method developed in this project are the following:

Identification of partial functions which can be used with advantage in several circuit components. This works by exploiting some degrees of freedomu when selecting decomposition functions. When realizing functions with multiple outputs one must have in mind that as many common decomposition functions as possible are computed.

Identification of partial functions which can be used with advantage in several circuit components. This works by exploiting some degrees of freedomu when selecting decomposition functions. When realizing functions with multiple outputs one must have in mind that as many common decomposition functions as possible are computed.

Exploiting symmetries.

Exploiting symmetries.

Exploiting don't cares in partial functions.

Exploiting don't cares in partial functions.

|

Paul Molitor, Prof. Dr., Christoph Scholl, Prof. Dr. Communication based multilevel synthesis for multi-output boolean functions Great Lakes Symposium on VLSI, 1994 |

|

Christoph Scholl, Prof. Dr., Paul Molitor, Prof. Dr. Efficient ROBDD based computation of common decomposition functions of multi-output boolean functions IFIP Workshop on Logic and Architecture Synthesis, 1994 |

|

Christoph Scholl, Prof. Dr., Paul Molitor, Prof. Dr. Efficient ROBDD based computation of common decomposition functions of multi-output boolean functions Logic and Architecture Synthesis, State-of-the-art and novel approaches, 1995 |

|

Christoph Scholl, Prof. Dr., Paul Molitor, Prof. Dr. Communication Based FPGA Synthesis for Multi-Output Boolean Functions Asia and South Pacific Design Automation Conference, 1995 |

|

Christoph Scholl, Prof. Dr. University of Saarland, Ph.D. thesis, 1996 |

|

Christoph Scholl, Prof. Dr. Functional Decomposition with Integrated Test Generation GI/ITG Workshop ``Testmethoden und Zuverlässigkeit von Schaltungen und Systemen´´, 1997 |

|

Christoph Scholl, Prof. Dr., Stefan Melchior, Günter Hotz, Paul Molitor, Prof. Dr. Minimizing ROBDD Sizes of Incompletely Specified Functions by Exploiting Strong Symmetries Proceedings of the European Design and Test Conference, 1997 |

|

Christoph Scholl, Prof. Dr. Multi-output Functional Decomposition with Exploitation of Don't Cares In Proceedings of IWLS, 1997 |

|

Christoph Scholl, Prof. Dr. Multi-output Functional Decomposition with Exploitation of Don't Cares In Proceedings of DATE, 1998 |

|

Christoph Scholl, Prof. Dr., Dirk Möller, Paul Molitor, Prof. Dr., Rolf Drechsler, Prof. Dr. BDD Minimization Using Symmetries IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 1999 |