# Schritte der Analyse: 1. Timing der Register-PALs (Setup – [Hold] – Zeiten) 2. Vermeidung von Bus-Contention 3. PC-Inkrementierung 4. Compute-Befehle O.E.: Compute Memory mit D = PC (Setup + Hold – Zeiten länger als bei Reg.) (auch kritischer als Fetch!) 5. Load, Store O.E.: LOADIN1, STOREIN1 6. JUMP

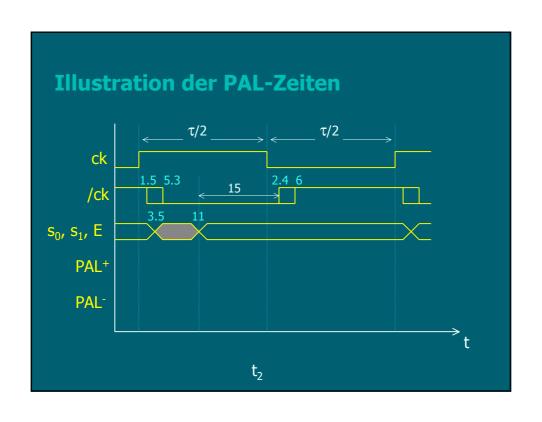

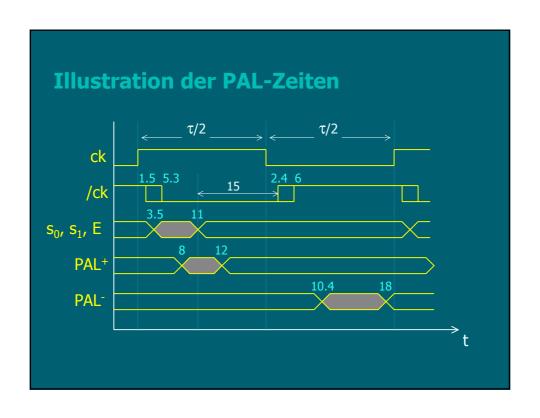

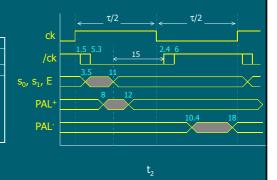

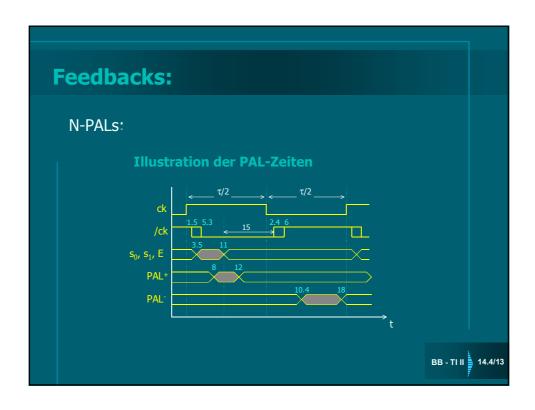

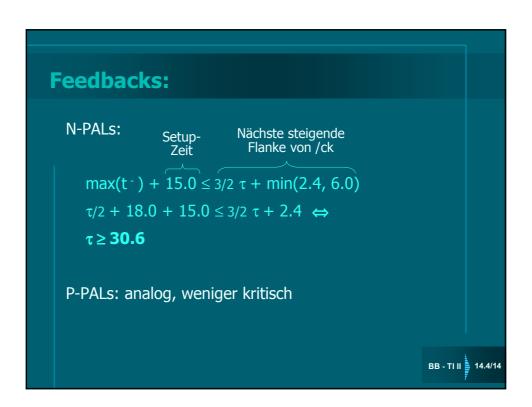

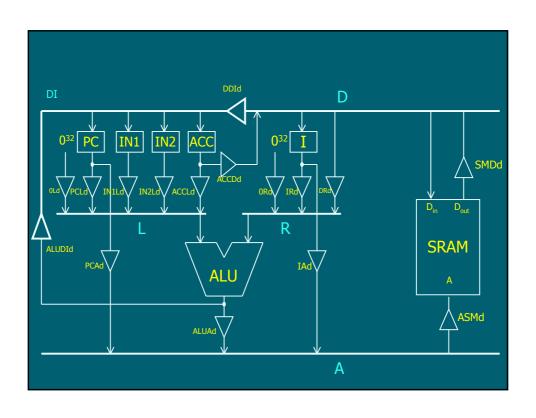

# 14.4.1 Timing der Register-PALs P-PALs = PALs, die mit ck getaktet werden N-PALs = PALs, die mit /ck getaktet werden ( Illustration siehe folgende Abbildung oder Datenblatt für PALs! )

### **Schaltzeiten der PALs 20Rxx und 20Lxx**

| Symbol             | Name                                              | min  | max  |

|--------------------|---------------------------------------------------|------|------|

| t <sub>p</sub>     | Prop.Delay von Input oder Feedback nach<br>Output | 12.0 | 15.0 |

| t <sub>CLK</sub>   | Prop.Delay von CK nach Output oder Feedback       | 8.0  | 12.0 |

| t <sub>C</sub>     | Zykluszeit ohne Feedback                          | 22.2 |      |

| t <sub>C</sub>     | Zykluszeit mit Feedback                           | 27.0 |      |

| $t_{s}$            | Setup-Zeit von Input oder Feedback bis CK         | 15.0 |      |

| t <sub>H</sub>     | Hold-Zeit                                         | 0.0  |      |

| t <sub>w</sub> (H) | Clockpulsweite                                    | 12.0 |      |

| t <sub>w</sub> (L) |                                                   | 10.0 |      |

### Ausgänge der PALs

Ausgänge von P-PALs gültig zur Zeit

$$t + = (8.0, 12.0)$$

Propagation Delay von ck bis PAL-Ausgänge

Ausgänge von N-PALs gültig zur Zeit

$$t^{-} = \tau/2 + (2.4, 6.0) + (8.0, 12.0) = \tau/2 + (10.4, 18.0)$$

Propagation Delay PAL

Inverter

### **Input-Signale von Register-PALs:**

Zählerausgänge s0, s1, E, Registerausgänge von I, Feedbacks bei Haltetermen

Für P-PALs: auch ACC, ZL, ZH (JUMP!)

→ Timing-Bedingungen aus Setup-Zeiten

BB - TI II 14.4/9

■ Zählerausgänge s0, s1, E als PAL-Eingänge:

O.E.: Betrachte N-PALs

(bei P-PALs hat man  $\tau/2$  länger Zeit!)

### Schaltzeiten der PALs 20Rxx und 20Lxx

| Symbol             | Name                                              | min  | max  |

|--------------------|---------------------------------------------------|------|------|

| t <sub>p</sub>     | Prop.Delay von Input oder Feedback nach<br>Output | 12.0 | 15.0 |

| t <sub>CLK</sub>   | Prop.Delay von CK nach Output oder Feedback       | 8.0  | 12.0 |

| t <sub>c</sub>     | Zykluszeit ohne Feedback                          | 22.2 |      |

| t <sub>c</sub>     | Zykluszeit mit Feedback                           | 27.0 |      |

| t <sub>s</sub>     | Setup-Zeit von Input oder Feedback bis CK         | 15.0 |      |

| t <sub>H</sub>     | Hold-Zeit                                         | 0.0  |      |

| t <sub>w</sub> (H) | Clockpulsweite                                    | 12.0 |      |

| t <sub>w</sub> (L) |                                                   | 10.0 |      |

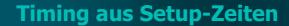

### **Timing aus Setup-Zeiten**

- Zählerausgänge s0, s1, E als PAL-Eingänge:

- O.E.: Betrachte N-PALs

(bei P-PALs hat man  $\tau/2$  länger Zeit!)

$\blacksquare$  max(3.5, 11.0) + 15.0  $\leq \tau/2$  + min(2.4, 6.0)

Propagation Delay Setup-Zeit von ck bis PAL Zählerausgänge

$\rightarrow \tau \geq 47.2$

BB - TI II 14.4/11

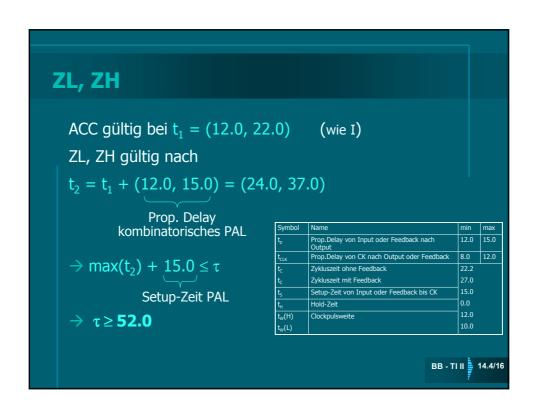

### **Timing aus Setup-Zeiten (ff)**

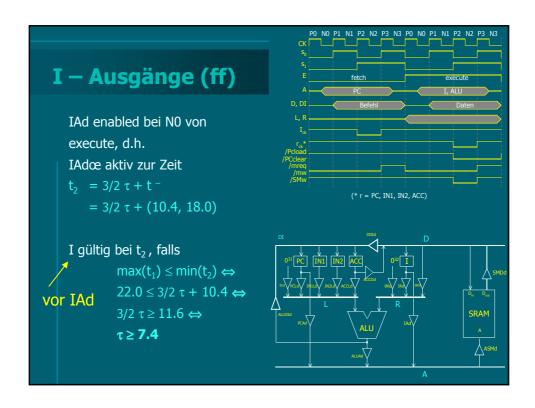

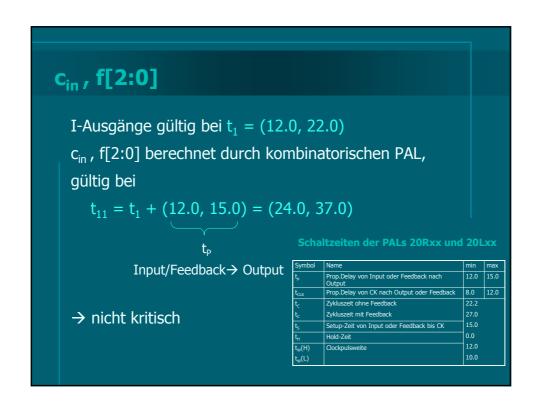

Registerausgänge von I als PAL-Eingänge:

O.E.: N-PALs

I-Ausgänge gültig bei  $t_1 = t^+ + (4.0, 10.0) = (12.0, 22.0)$

Clock Ick Verzögerung 74F374

$max(12.0, 22.0) +15.0 \le \tau/2 + min(2.4, 6.0)$

Prop. Delay von ck bis I-Ausgänge

$\rightarrow$  34.6  $\leq$   $\tau$ /2  $\Leftrightarrow$   $\tau \geq$  **69.2**

# Analog I, weniger kritisch, da nur Eingang von P-PALs

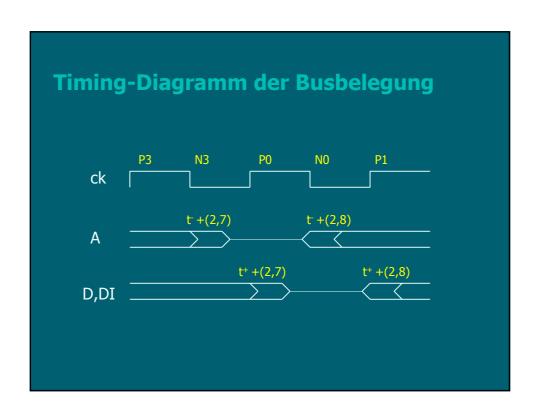

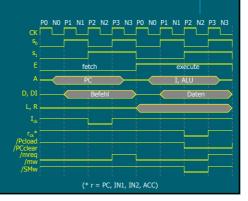

# 14.4.2 Vermeidung von Bus Contention BB-TII 14.4/17

Timing der Busbelegung: N-PALs

$$\max(t^- + (2.0,7.0)) \le \tau + \min(t^- + (2.0,8.0))$$

$$\text{disable-Zeit}$$

$$\text{enable-Zeit}$$

$$\frac{\tau}{2} + 25.0 \le \tau + \frac{\tau}{2} + 12.4$$

$$\rightarrow \qquad \tau \ge 12.6 \text{ ns}$$

Timing der Busbelegung: P-PALs

$$max(t^{+} + (2.0,7.0)) \leq \tau + min(t^{+} + (2.0,8.0))$$

$$disable-Zeit$$

$$19.0 \leq \tau + 10.0$$

$$\Rightarrow \qquad \tau \geq 9.0 \text{ ns}$$

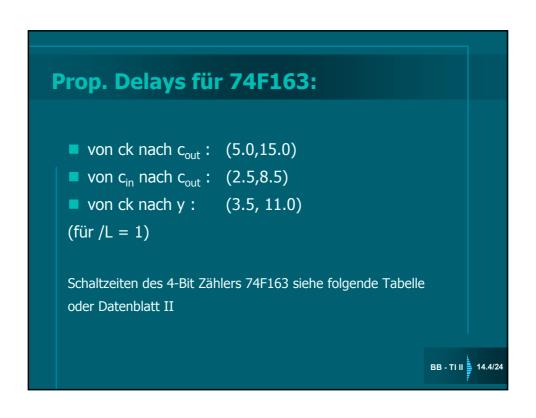

| Symbol              | Name                                                  | min  | max  |

|---------------------|-------------------------------------------------------|------|------|

| t <sub>c</sub>      | Zykluszeit                                            | 11.1 |      |

| t <sub>PLH</sub>    | Prop. Delay von ck nach y <sub>i</sub>                | 3.5  | 8.5  |

| t <sub>PHL</sub>    | wenn /L = 1                                           | 3.5  | 11.0 |

| t <sub>PLH</sub>    | Prop. Delay von ck nach y <sub>i</sub>                | 4.0  | 9.5  |

| t <sub>PHL</sub>    | wenn /L = 0                                           | 4.0  | 9.5  |

| $t_{PLH} = t_{PHL}$ | Prop. Delay von ck nach c <sub>out</sub>              | 5.0  | 15.0 |

| $t_{PLH} = t_{PHL}$ | Prop. Delay von c <sub>in</sub> nach c <sub>out</sub> | 2.5  | 8.5  |

| $t_S(H) = t_S(L)$   | Setup-Zeit von x <sub>i</sub> nach ck                 | 5.0  |      |

| $t_H(H) = t_H(L)$   | Hold-Zeit von x <sub>i</sub> nach ck                  | 2.0  |      |

| t <sub>S</sub> (H)  | Setup-Zeit von /L oder /C bis                         | 11.5 |      |

| t <sub>S</sub> (L)  | ck                                                    | 9.5  |      |

| t <sub>H</sub> (H)  | Hold-Zeit von /L oder /C nach                         | 2.0  |      |

| t <sub>H</sub> (L)  | ck                                                    | 0.0  |      |

| t <sub>S</sub> (H)  | Setup-Zeit von c <sub>in</sub> bis ck                 | 11.5 |      |

| t <sub>S</sub> (L)  |                                                       | 5.0  |      |

| $t_H(H) = t_H(L)$   | Hold-Zeit von c <sub>in</sub> bis ck                  | 0.0  |      |

| $t_W(H) = t_W(L)$   | Clockpulsweite (Zählen)                               | 5.0  |      |

| t <sub>H</sub> (H)  | Clockpulsweite (Laden)                                | 4.0  |      |

| t <sub>H</sub> (L)  |                                                       | 7.0  |      |

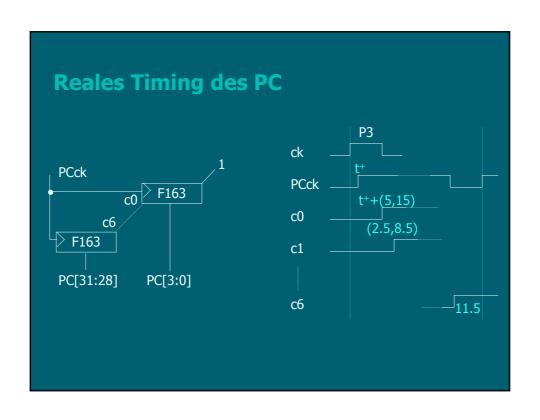

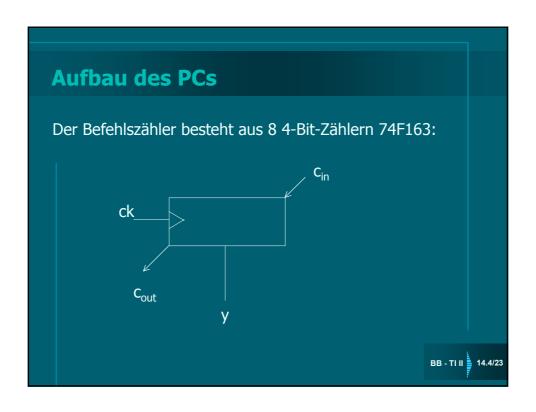

### **Berechnung der PC-Clock**

PCck wird durch P-PAL berechnet mit steigender Flanke bei P3 von Execute:

$$t^+ = (8.0, 12.0)$$

( P3 ist zeitlicher Bezugspunkt! )

→ Für  $0 \le i \le 6$  wird  $c_i$  gültig bei

$$\xi_i = t^+ + (5,15) + i \cdot (2.5,8.5)$$

### **Bedingungen:**

Folgende Bedingungen müssen eingehalten werden:

1. Hold-Zeit von c<sub>i</sub> nach PCck: 0.0 ns

BB - TI II 14.4/27

### **Bedingungen: (ff)**

2. Setup-Zeit von  $c_i$  bis PCck = 11.5 ns

$$\max_{0 \leq i \leq 6} \left\{ max(\xi_i) \right\} + 11.5 \leq 8\tau + \min(t^+)$$

bei nächstem PAL-Delay für PCck

$$\Leftrightarrow \text{max}(\xi_6) + 11.5 \leq 8\tau + 8.0$$

$$\Leftrightarrow 12.0 + 15.0 + 6 \cdot 8.5 + 11.5 \leq 8\tau + 8.0$$

$$\Rightarrow \tau \ge 10.2 \text{ ns}$$

Bedingungen: (ff)

3. Änderung der PC-Ausg. abgeschlossen, wenn PCAd bei N0 von Fetch enabled wird.

$$\max(t^+) + 11.0 \le \frac{3}{2}\tau + \min(t^-)$$

$$\text{Zeit für PCck} \qquad \text{PCAdœ}$$

$$\text{Delay PCck} \qquad \text{Delay PCck} \qquad \text{Dis NO}$$

$$\text{Ausgänge} \qquad \text{Fetch}$$

$$\Rightarrow \tau \ge 8.4 \text{ ns}$$

$$\Rightarrow \text{PC - Inkrementieren ist unkritisch!}$$

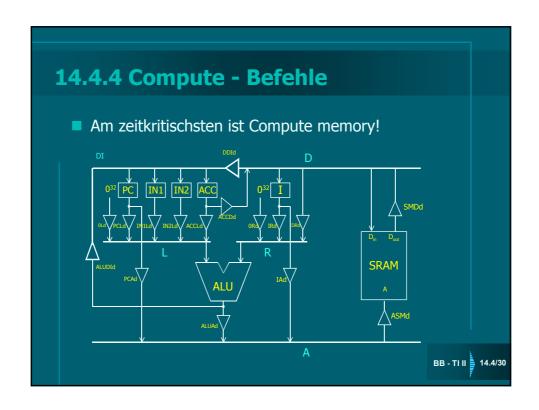

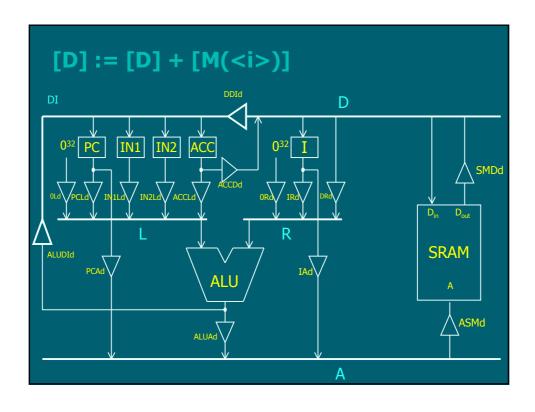

### Als Voraussetzung für exaktes Timing von Compute memory

- Analyse unserer kaskadierten ALU unter folgenden Annahmen

- Operanden und c<sub>in</sub> sind bei t<sub>0</sub> gültig,

- Funktionsselect-Signal bei  $t_0 7.0$ .

ergibt:

→ (Übung)

Resultatsausgänge gültig bei

$$t_{ALU} = t_0 + 83.5 \text{ ns}$$

BB - TI II 14.4/33

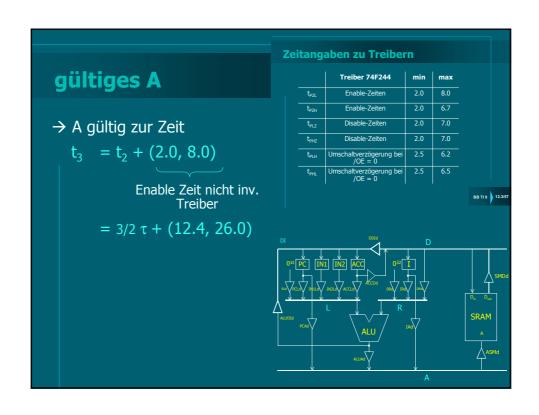

### **Analyse allgemein**

- Beginn der Analyse bei P3 von fetch als zeitlicher Bezugspunkt

- Ick des Instruktionsregisters hat steigendeFlanke bei P3 von fetch.

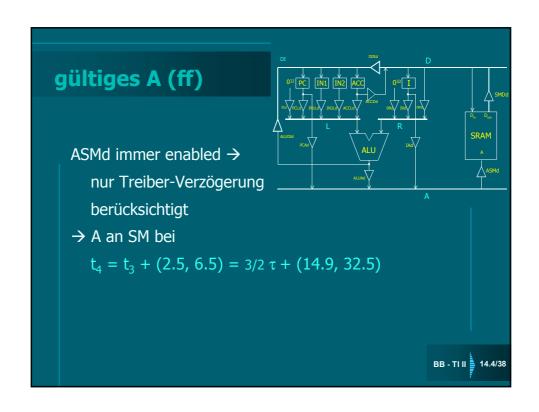

# Daten am Speicherausgang Lesezugriffszeit von SM: (3.0, 45.0) ( $\rightarrow$ CY7C 191 – 45) AGültige Daten am ASpeicherausgang bei $t_5 = t_4 + (3.0, 45.0)$ $= 3/2 \tau + (17.9, 77.5)$

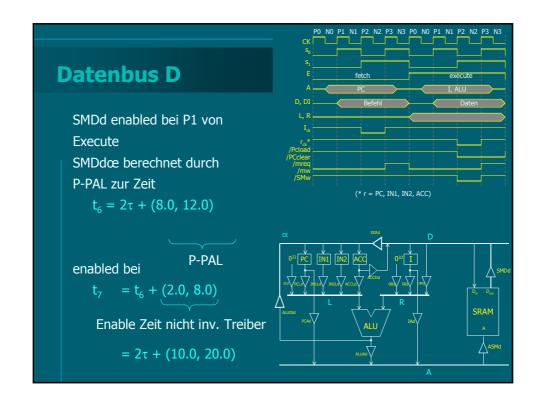

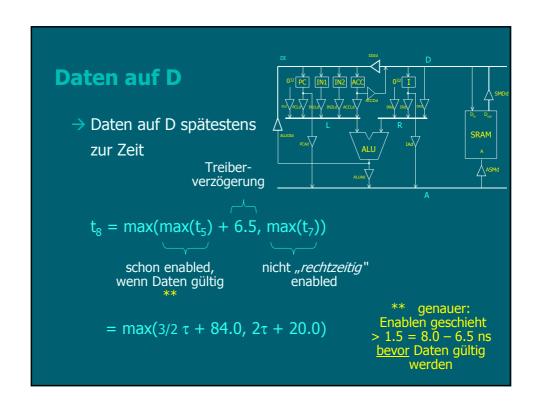

# Datenbus D (ff) Bei langsamem Takten sind Daten schon bereit beim Enablen, bei schnellem Takten noch nicht!

```

Daten auf L (ff)

L gültig zur Zeit

t_{10} = \tau + (8.0, 12.0) + (2.0, 12.5) = \tau + (10.0, 24.5)

Delay P-PAL worst case:

Delay der internen Treiber von IN1, IN2

**

( \Rightarrow nicht kritisch!)

**

T4F374 interne Treiber; alle anderen externe Treiber ([2,8])

```

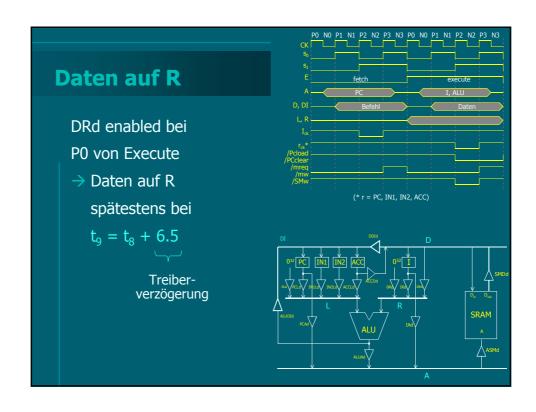

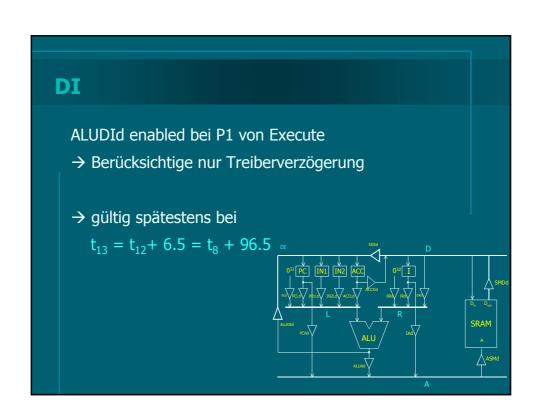

ALU — Ausgänge spätestens gültig bei

$$t_{12} = t_9 + 83.5 = t_8 + 90.0 = \max(3/2 \tau + 84.0, 2\tau + 20.0) + 90$$

Delay ALU

$$t_{10} \quad t_9 = t_8 + 6.5 \quad t_{11}$$

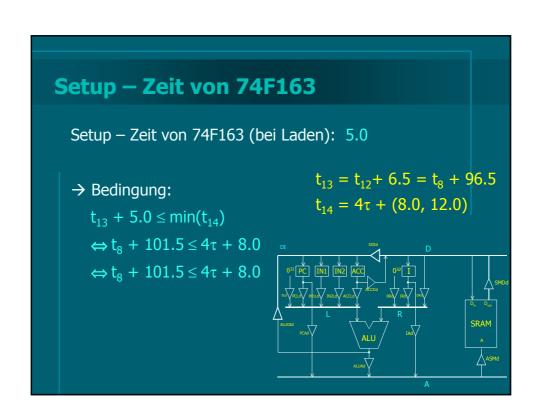

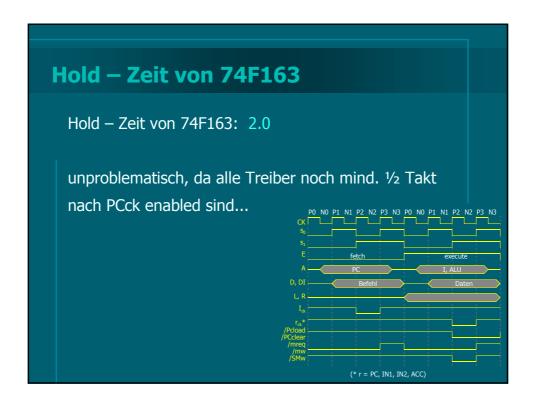

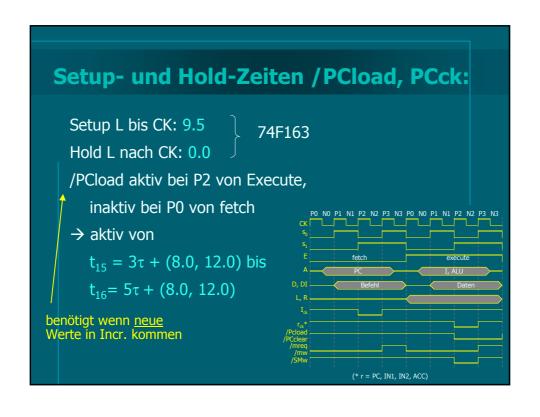

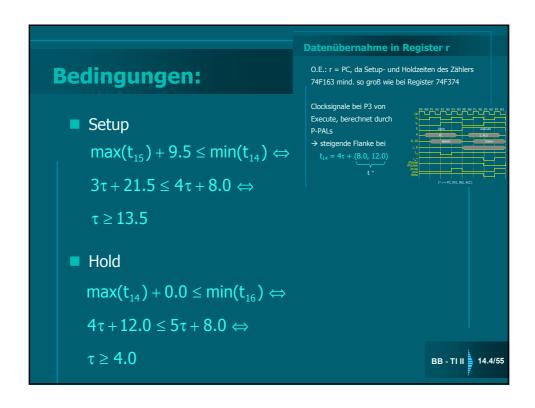

# Datenübernahme in Register r O.E.: r = PC, da Setup- und Holdzeiten des Zählers 74F163 mind. so groß wie bei Register 74F374 Clocksignale bei P3 von Execute, berechnet durch P-PALs $\Rightarrow$ steigende Flanke bei $t_{14} = 4\tau + (8.0, 12.0)$

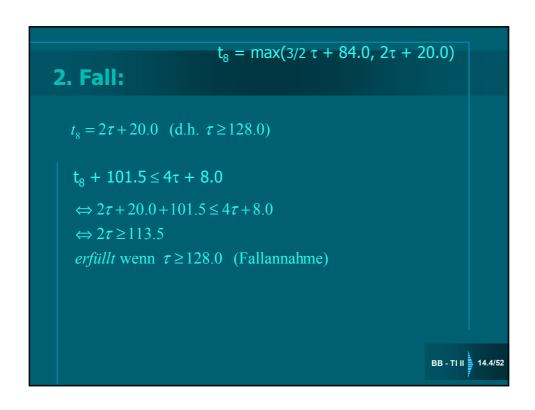

$$t_8 = \max(3/2 \ \tau + 84.0, 2\tau + 20.0)$$

**1. Fall:**

$$t_8 = \frac{3}{2}\tau + 84.0 \quad (\text{d.h.} \ \frac{3}{2}\tau + 84.0 \ge 2\tau + 20.0 \Leftrightarrow \tau \le 128.0)$$

$$t_8 + 101.5 \le 4\tau + 8.0$$

$$\Leftrightarrow \frac{3}{2}\tau + 185.5 \le 4\tau + 8.0$$

$$\Leftrightarrow \frac{5}{2}\tau \ge 177.5$$

$$\Leftrightarrow \tau \ge 71.0$$

```

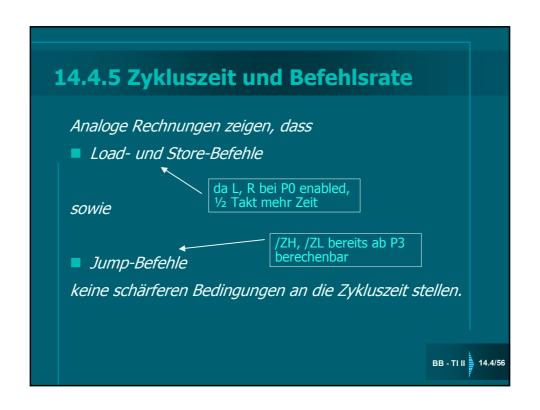

Zykluszeit und Befehlsrate (ff)

Zykluszeit:

\tau \ge 71.0 \text{ ns}

Taktfrequenz:

v = \frac{1}{71} \cdot 10^9 \text{ Hz} = 14.1 \text{ MHz}

8 Takte pro Befehl \rightarrow

1.76 Millionen Befehle pro Sekunde,

d.h. Befehlsrate von 1.76 MIPS

( = Million Instructions Per Second )

```