#### **Ausblick**

Bisher wurden nur kombinatorische Schaltkreise

$$SK = (\vec{X}_n, G, typ, in, out, \vec{Y}_m)$$

betrachtet, wobei G azyklisch war.

Was geschieht, wenn G nicht zykelfrei ist?

→ Schalt<u>pläne</u>, Schaltungen

# Vorgehen

- Exkurs über physikalische Eigenschaften von Gattern → "Approximation" des Zeitverhaltens

- Analyse spezieller Schaltpläne mit Zyklen, nämlich Speicherbausteine wie z.B. Flipflops, Latches, Register, RAMs, ROMs, ...

- Betrachte nur noch bestimmte Teilklassen von Schaltplänen: Zusammenschaltungen von Speicherbausteinen und Schaltkreisen nach bestimmten Regeln

- → sequentielle SKs bzw. Schaltwerke

- Diskreter Aufbau eines gesamten Rechners (Kap. 13 ff) mit Analyse des Zeitverhaltens

- → Einsicht in die Funktionsweise eines Rechners (und z.T. auch in die eines Entwurfssystems)

BB TI II 12.1/3

#### 12.1 Physikalische Eigenschaften und Timing

Bernd Becker - Technische Informatik II

#### Physikalische Eigenschaften von **Gattern**

3 wesentliche Punkte:

- 1. logische Signale ≅ Spannungspegel

- 2. Fanout von Gattern ist begrenzt

- 3. Gatter benötigen Zeit zum Schalten!!

BB TI II 12.1/5

#### **Beispiel:**

Notation zur Kennzeichnung von Bausteinen:

Technologie

Funktion des Bausteins

BB TI II 12.1/6

#### **Beispiel: (ff)**

Bausteinfamilie FAST (Fairchild Advanced Schottky TTL) (spezifiziert in FAST DATA BOOK, 1985)

Bsp: 54F04 =

Chip mit 6 Invertern in FAST Technologie, militärischer Bereich

BB TI II 12.1/7

#### **Zur Notation:**

####

- Temperaturbereich, Störanfälligkeit gegen Strahlung, Ausfallsicherheit

- 54 = militärischer Bereich

- 74 = kommerzieller Bereich

#### y y y:

Funktion unabhängig von Technologie und Betriebssystem

#### <u>W:</u>

F: FAST = Fairchild Advanced Schottky TTL

FACT: Fairchild Advanced **CMOS Technology**

TTL: Transistor-Transistor Logic

LS: Low Power Schottky

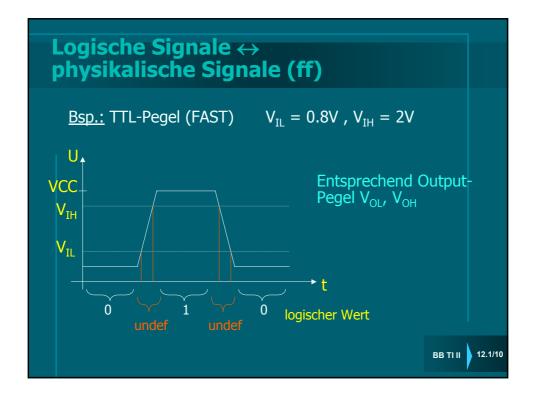

# **Logische Signale** ↔ **physikalische Signale**

In jeder Technologie gibt es eine Versorgungsspannung VCC (z.B. VCC = 5V).

Zwei Input-Pegel: $V_{IH}$  (V in high) und  $V_{IL}$ (V in low)

$\rightarrow$  Eine Spannung U  $\in$  [0, VCC] am Eingang eines Gatters wird als logischer Wert I(U) interpretiert.

$$I(U) = \begin{cases} 0 & \text{, falls } U \leq V_{IL} \\ 1 & \text{, falls } U \geq V_{IH} \\ \text{undef. , sonst} \end{cases}$$

BB TI II 12.1/9

#### **Beispiel zum Output**

FAST-Bausteine mit  $V_{OL} \in [0.5, 0.55], V_{OH} \in [2, 2.7]$ Will man Ausgang u eines Gatters mit Eingang v verbinden, dann sollte gelten:

$$V_{\text{OL}}^{\text{u}} \leq V_{\text{IL}}^{\text{v}}$$

,  $V_{\text{OH}}^{\text{u}} \geq V_{\text{IH}}^{\text{v}}$  ,

sonst werden Signale falsch interpretiert.

**Bsp.:** FAST benutzt TTL-Pegel

→ Hintereinanderschalten möglich

BB TI II 12.1/11

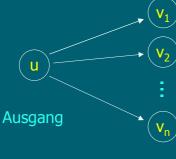

# **Fanout – graphisch veranschaulicht**

Gattereingänge

#### **Fanout bei FAST**

Falls am Ausgang u Spannung U anliegt, dann gilt (Kirchhoff'sches Gesetz):

$$I(U) = \sum_{j=1}^{n} I^{j}(U)$$

(I(U) = Stromstärke an Ausgang u, $I^{j}(U) = Stromstärke an Eingang v_{i}$

v<sub>i</sub> verbrauchen Strom, aber u kann nicht unbegrenzt Strom liefern!!

BB TI II 12.1/13

#### Fanout bei FAST ff.

In Katalogen nur

- (Ausgangsstrom bei Signal ■ I<sub>OL</sub>, I<sub>OH</sub> für Ausgänge low/high)

- I<sub>IL</sub>, I<sub>IH</sub> für Eingänge (Eingangsstrom für Signal low/high)

- $\Rightarrow$   $v_1, ..., v_n$  wird nur dann an u angeschlossen, wenn  $I_{OL} \ge \sum_{i=1}^{n} I_{IL}^{j}$ ,  $I_{OH} \ge \sum_{i=1}^{n} I_{IH}^{j}$

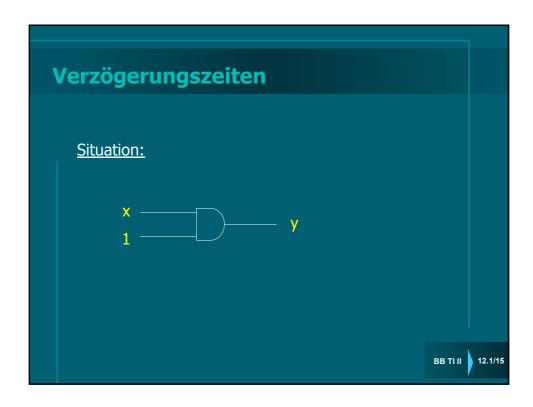

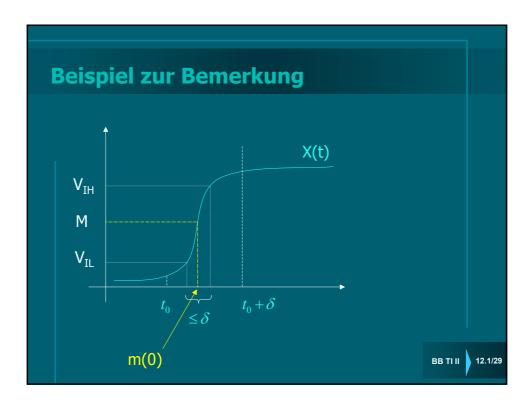

# Allgemeine Bemerkung zu Verzögerungszeiten

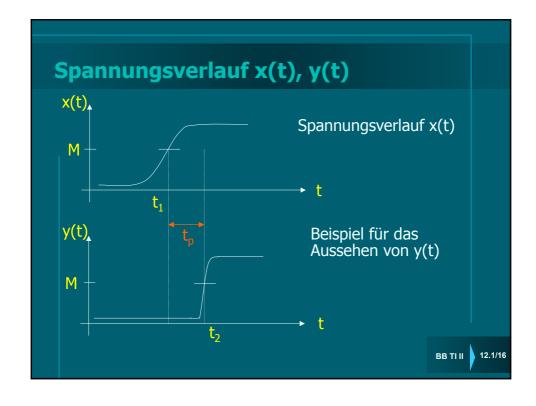

Im allgemeinen gilt <u>nicht</u>  $y(t) = x(t-t_p)$ , so dass man dann einfach  $t_p$  als Verzögerungszeit definieren kann. y(t) wird <u>verformt</u>.

<u>Hier:</u> Verzögerungszeit bzgl. einer festen Spannung M mit  $V_{\text{IL}} < M < V_{\text{IH}}$

Bestimme  $t_1$ ,  $t_2$  mit  $x(t_1) = y(t_2) = M$

$\rightarrow$  t<sub>p</sub> = t<sub>2</sub> - t<sub>1</sub> (*propagation delay* = Verzögerungszeit)

BB TI II 12.1/17

# Beispiel

FAST-Bausteine für M = 1.5V spezifiziert.

Bausteine 74F00, 74F04, 74F08, 74F32, 74F86:

(NAND, NOT, AND, OR, EXOR)

$t_n$  zwischen 1.5 und 8.0 ns (1 ns =  $10^{-9}$ s)

#### Angaben zur Verzögerungszeit

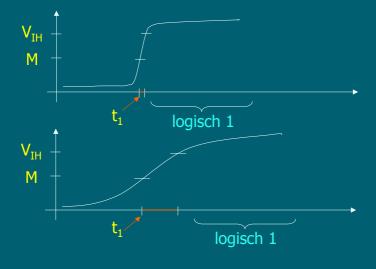

In der Regel verschiedene Verzögerungszeiten für Übergänge  $0 \rightarrow 1$  und  $1 \rightarrow 0$ .

Daher nicht t<sub>n</sub> angegeben, sondern

- $t_{PLH}$ : Verzögerungszeit bei  $0 \rightarrow 1$

- $t_{PHI}$ : Verzögerungszeit bei  $1 \rightarrow 0$

BB TI II 12.1/19

## Modellierung der Verzögerungszeit

Problem bei Modellierung der Verzögerungszeit bzgl. fester Spannung M:

Keine Aussage darüber, wann logische Signale 0 bzw. 1 sind, d.h. physikalische Signale unterhalb V<sub>II</sub> bzw. oberhalb V<sub>IH</sub> sind.

## **Anstiegs- und Abfallzeit**

Für jedes Signal braucht man also zusätzliche Informationen über:

- Anstiegszeit (rise time) = Zeit, in der Signal von  $V_{\text{\scriptsize IL}}$  nach  $V_{\text{\scriptsize IH}}$  steigt

- Abfallzeit (fall time) = Zeit, in der Signal von  $V_{IH}$  nach  $V_{IL}$  fällt

#### Beschränkung dieser Zeiten

Die in unseren Analysen verwendeten Gatter haben die folgende angenehme Eigenschaft:

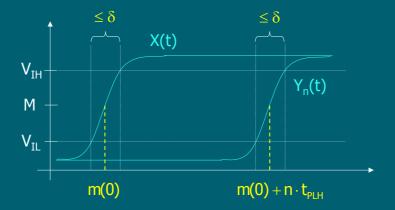

$\exists \ \delta$  mit folgender Eigenschaft:

Falls rise/fall time  $\leq \delta$  am Gattereingang, dann rise/fall time  $\leq \delta$  am Gatterausgang.

Bsp.: FAST-Bausteine:  $\delta \approx 2.5$  ns

BB TI II 12.1/23

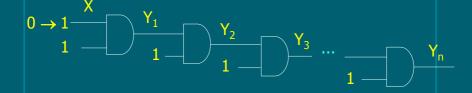

#### Analyse der Verzögerungszeit einer Kette von *n* Gattern

#### Analyse der Verzögerungszeit einer Kette von *n* Gattern (ff)

#### Analyse der Verzögerungszeit einer **Kette von** *n* **Gattern (ff)**

Durchläuft X(t) nach Zeit m(0) die Spannung M, dann durchläuft Y<sub>n</sub>(t) die Spannung M nach  $m(0) + n \cdot t_{PIH}$ .

Falls X(t) mit Anstiegszeit  $\leq \delta$ , dann auch  $Y_1(t)$ , ...,  $Y_n(t)$ .

Also ist Y<sub>n</sub> auf jeden Fall zur Zeit  $m(0) + n \cdot t_{PLH} + \delta$  logisch 1.

## **Allgemein:**

Die Zeiten, an denen die entsprechenden Signale wohldefinierte logische Werte 0, 1 annehmen, unterscheiden sich von denen für M um höchstens  $\delta$ .

BB TI II 12.1/27

## **Bemerkung:**

Eine rise/fall time  $\leq \delta$  an den primären Eingängen einer Schaltung kann man garantieren, wenn man den Schaltvorgang zur Zeit t<sub>0</sub> beginnt und spätestens zur Zeit  $t_0 + \delta$  abschließt.

# **Bemerkung (ff)**

Beginnt man im Beispiel den Schaltvorgang bei t<sub>0</sub> und beendet ihn bei  $t_0 + \delta$  ,  $dann \ gilt \ m(0) \leq t_0 + \delta$ und Y<sub>n</sub> ist spätestens nach  $t_0^{} + n \cdot t_{\mathsf{PLH}}^{} + 2\delta$ logisch 1.

#### **Vereinbarung:**

Im folgenden soll

Signal X wird zum Zeitpunkt t<sub>1</sub> abgesenkt/angehoben bedeuten

X wird abgesenkt/angehoben mit  $X(t_1) = M$ .

BB TI II 12.1/31

#### **Kapazitive Last**

Verzögerungszeiten von Gattern sind nicht konstant, sondern werden beeinflusst durch

- Betriebstemperatur

- Fertigungsprozess des Chips

- kapazitive Last am Gatterausgang

#### **Kapazitive Last (1)**

Kapazitive Last am Ausgang u entsteht dadurch, dass sich die Eingänge  $v_1$ , ...,  $v_n$ , die mit u verbunden sind, wie Kondensatoren verhalten, die beim Schalten ge- bzw. entladen werden müssen.

BB TI II 12.1/33

#### **Kapazitive Last (2)**

Zusätzlich wird auch der Leitung zwischen u und v₁ (∀i) eine kapazitive Last zugeordnet.

Einheit für kapazitive Lasten:

1 Farad (1 F)

Jedem Eingang von Gattern wird eine kapazitive Last zugeordnet. (FAST: 4 – 5 pF)

#### **Kapazitive Last (3)**

Für die Gesamtlast C an u gilt:

$$C = C_L + \sum_{j=1}^{n} C_j$$

$$C = \sum_{j=1}^{n} C_j$$

$$C = \sum_{i=1}^{n} C_{i}$$

falls die Leitungskapazität ignoriert werden kann.

Dies ist auf Leiterplattenebene in der Regel der Fall.

BB TI II 12.1/35

## **Kapazitive Last (4)**

Verzögerungszeiten t<sub>D</sub> werden in der Regel für eine Standardlast C<sub>0</sub> angegeben.

(FAST: 50 pF)

Ist  $C \neq C_0$ , so gilt:

$$t_p(C) = t_p(C_0) + \alpha_u \cdot (C - C_0)$$

mit  $\alpha_u$  technologieabhängige Konstante

FAST:  $\alpha_u = 0.03 \frac{ns}{nF}$

#### **Kapazitive Last (5)**

#### Abschätzung:

Wieviele Eingänge kann man an Ausgänge hängen, ohne dass  $t_n(C_0)$  überschritten wird?

BB TI II 12.1/37

## **Kapazitive Last (6)**

#### Annahme:

$C_{max} = 5 pF für jeden Eingang.$

Hängt man maximal  $n_0 = \frac{C_0}{C_{max}} = \frac{50 \, pF}{5 \, pF} = 10$

Eingänge an einen Ausgang, so gilt

$$C = \sum_{i=1}^{n} C_i \le n \cdot C_{max} \le n_0 \cdot C_{max} = C_0$$

und damit  $t_p(C) \le t_p(C_0)$

→ Fanoutbeschränkung ≤ 10 für FAST-Bausteine

#### **Worst-case Timing-Analyse**

Wegen Abhängigkeit der Verzögerungszeit von Temperatur oder Fertigungsprozess werden vom Hersteller keine festen Zeiten t<sub>PI H</sub>/t<sub>PHI</sub> angegeben, sondern 3 Werte:

- $\tau^{min}$  = untere Schranke

- $\tau^{\text{max}}$  = obere Schranke

- $\mathbf{v}^{\mathsf{typ}} = \mathsf{typischer} \, \mathsf{Wert} \, \, (???)$

BB TI II 12.1/39

#### min, max und typ

Bei Temperaturen im Bereich T (kommerzieller Temperaturbereich 0° - 70° C, militärischer Temperaturbereich -55° - 125° C) und Last C<sub>0</sub> gilt für tatsächliche Verzögerungszeit t<sub>n</sub>:

$$\tau^{\text{min}} \leq t_{_{D}} \leq \tau^{\text{max}}$$

#### min, max und typ (ff)

Für  $\tau^{\text{typ}}$  gilt ebenfalls  $\tau^{\min} \leq \tau^{\text{typ}} \leq \tau^{\max}$ . Beim Rechnen mit  $\tau^{typ}$  macht man einen Fehler mit unbekannter Größe.

$\rightarrow$  kein Rechnen mit  $\tau^{typ}$ , sondern mit Intervallen  $(\tau^{\min}, \tau^{\max})$

BB TI II 12.1/41

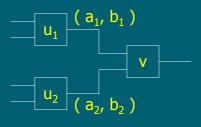

# Zeitintervalle bei Timing-Analysen

- zur Zeit (a, b) heißt: frühestens zur Zeit a, spätestens bei b

- zur Zeit a ≅ zur Zeit ( a, a )

- $\blacksquare$  min (a, b) = a, max(a,b) = b,(a, b) + (c, d) = (a+c, b+d)

# **Beispiel: AND-Gatter**

AND - Gatter (74F08):

|                  | min | max |

|------------------|-----|-----|

| t <sub>PLH</sub> | 3.0 | 6.6 |

| t <sub>PHL</sub> | 2.5 | 6.3 |

BB TI II 12.1/43

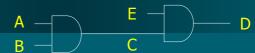

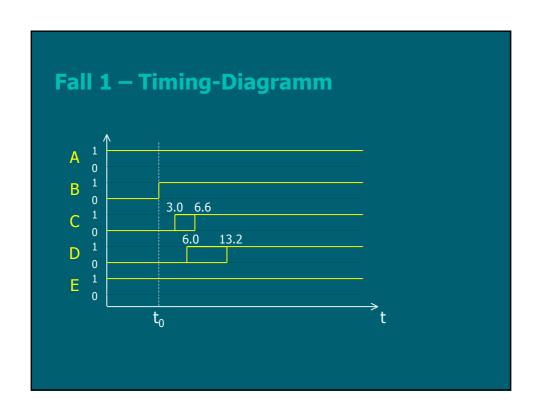

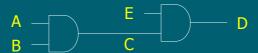

#### Fall 1

- A, E fest auf 1

- B von 0 auf 1 zum Zeitpunkt t<sub>0</sub>

- → Änderung von C zur Zeit

$$t_1 = t_0 + (3.0, 6.6)$$

→ Änderung von D zur Zeit

$$t_2 = t_1 + (3.0, 6.6) = t_0 + (6.0, 13.2)$$

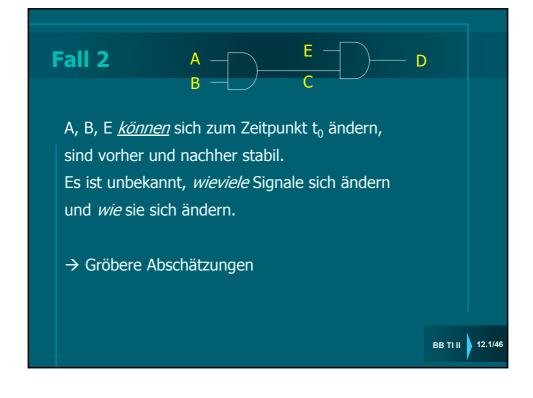

## Fall 2 (ff)

Bestimmung von Zeitintervallen, zu denen die Gatter überhaupt schalten können:

BB TI II 12.1/47

## Fall 2 (ff)

$$\begin{aligned} \text{Sei} \qquad t^{\text{min}} &:= \text{min} \left( \, \tau_{\text{LH}}^{\text{min}} \, , \, \tau_{\text{HL}}^{\text{min}} \, \right) \\ \\ t^{\text{max}} &:= \text{max} \left( \, \tau_{\text{LH}}^{\text{max}} \, , \, \tau_{\text{HL}}^{\text{max}} \, \right) \end{aligned}$$

gegeben für Gatter v.

→ v kann schalten zur Zeit  $(min (a_1, a_2), max (b_1, b_2)) + (t^{min}, t^{max})$

# **Im Beispiel:**

| AND              | min | max |

|------------------|-----|-----|

| t <sub>PLH</sub> | 3.0 | 6.6 |

| tou              | 2.5 | 6.3 |

Wenn die Gatter schalten, dann in folgenden Intervallen:

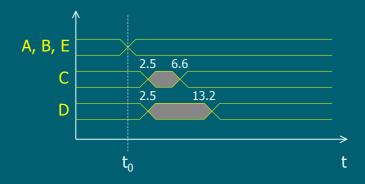

- $\blacksquare$  C:  $t_0 + (2.5, 6.6)$

- $\blacksquare$  E:  $t_0 + (0.0, 0.0)$

- D:  $(t_0 + 0.0, t_0 + 6.6) + (2.5, 6.6)$ =  $(t_0 + 2.5, t_0 + 13.2)$

BB TI II 12.1/49

# Fall 2 – Timing-Diagramm

#### **Interpretation des Timing-Diagramms**

Was kann im schraffierten Bereich passieren?

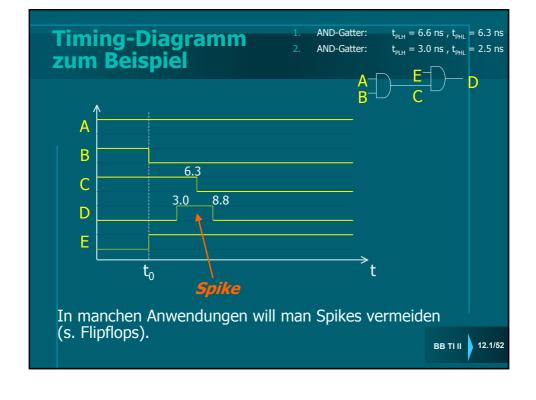

#### Beispiel:

$t_0$ : A, B, E:  $110 \rightarrow 101$

Annahme:

AND-Gatter haben folgende Verzögerungszeiten

1. AND-Gatter:  $t_{PLH} = 6.6 \text{ ns}$ ,  $t_{PHL} = 6.3 \text{ ns}$ 2. AND-Gatter:  $t_{PLH} = 3.0 \text{ ns}$ ,  $t_{PHL} = 2.5 \text{ ns}$

BB TI II 12.1/51

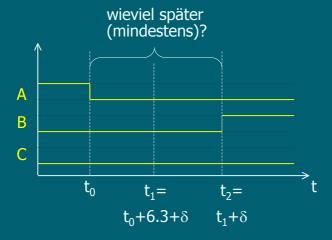

## Spikefreies Umschalten von Gattern

#### Ziel:

Übergang von A=1, B=0 zu A=0, B=1, ohne Spike am Ausgang.

#### Bemerkung:

Der Übergang ( 0, 1 )  $\rightarrow$  ( 1, 0 ) bzw. umgekehrt ist der einzige, bei dem an AND/NAND-Gattern ein Spike auftreten kann.

BB TI II 12.1/53

#### **Erinnerung:**

Signal s wird zum Zeitpunkt t gehoben/gesenkt heißt

s wird gehoben/gesenkt und durchläuft Spannung M dabei zum Zeitpunkt t.

#### **AND-Gatter:**

| AND              | min | max |

|------------------|-----|-----|

| t <sub>PLH</sub> | 3.0 | 6.6 |

| tou              | 2.5 | 6.3 |

#### **Timing im Gatter:**

| AND                | min | max |

|--------------------|-----|-----|

| $t_{\mathtt{PLH}}$ | 3.0 | 6.6 |

| tou                | 25  | 63  |

- 1. Senke A bei  $t_0 = 0$

- →Internes Schalten (bzgl. M!) spätestens nach 6.3 ns

- $\rightarrow$ C = 0 wegen A = 0 spätestens bei  $t_1 = t_0 + 6.3 + \delta$

- 2. Hebe B zum Zeitpunkt  $t_2 = t_1 + \delta$

$$\rightarrow$$

B = 0 zum Zeitpunkt t<sub>1</sub>

Also: Vor  $t_1$ :  $B = 0 \Rightarrow C = 0$

Nach  $t_1$ : C = 0 wegen A = 0

→ Übergänge für A und B mit Abstand

$$t_2 - t_0 = 6.3 + 2\delta = 11.3$$

# **NAND-Gatter:**

NAND – Gatter (74F00):

|                  | min | max |

|------------------|-----|-----|

| t <sub>PLH</sub> | 2.4 | 6.0 |

| t <sub>PHL</sub> | 1.5 | 5.3 |

Analog:

Abstand  $t_2 - t_0 = 11.0$

BB TI II 12.1/57